# **Temperature Sensor**

# With 2K Bits

# SPD EEPROM

Copyright © 2011 Giantec Semiconductor Inc. (Giantec). All rights reserved. Giantec reserves the right to make changes to this specification and its products at any time without notice. Giantec products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for critical medical or surgical equipment, aerospace or military, or other applications planned to support or sustain life. It is the customer's obligation to optimize the design in their own products for the best performance and optimization on the functionality and etc. Giante assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and prior placing orders for products.

### **Table of Contents**

| 1. Features                                  |    |

|----------------------------------------------|----|

| 1.1 The 2Kb SPD EEPROM Features              |    |

| 1.2 Temperature Sensor Features              |    |

| 2. General Description                       |    |

| 2.1 2K-bit SPD EEPROM                        | 4  |

| 2.2 Temperature Sensor                       | 4  |

| 3. Functional Block Diagram                  | 5  |

| 4. Pin Configuration                         |    |

| 4.1 8-Lead UDFN                              | 6  |

| 4.2 Pin Definition                           | 6  |

| 4.3 Pin Descriptions                         | 6  |

| 5. I <sup>2</sup> C / SMBus Serial Interface | 7  |

| 5.1 Serial bus interface                     |    |

| 5.2 I <sup>2</sup> C / SMBus Communication   | 7  |

| 5.3 Start Condition                          | 7  |

| 5.4 Stop Condition                           | 7  |

| 5.5 Acknowledge                              | 7  |

| 5.6 Slave address                            | 7  |

| 5.7 Power-Up and Reset States                | 8  |

| 6. Temperature Sensor                        | 11 |

| 6.1 TS Register Overview                     | 11 |

| 6.2 EVENT output                             |    |

| 6.3 Alarm window                             | 17 |

| 7. EEPROM Functional Description             |    |

| 7.1 Read and Write Operation                 |    |

| 7.2 Write Protection                         | 21 |

| 7.3 Reading Write Protection Status          | 21 |

| 8. Electrical Characteristics                |    |

| 8.1 Absolute Maximum Ratings                 | 24 |

| 8.2 Operating Range                          | 24 |

| 8.3 Capacitance                              | 24 |

| 8.4 DC Electrical Characteristic             |    |

| 8.5 AC Electrical Characteristic             |    |

| 9. Ordering Information                      |    |

| 10. Top Markings                             |    |

| 10.1 UDFN Package                            |    |

| 11. Package Information                      |    |

| 11.1 UDFN                                    |    |

| 12. Revision History                         |    |

### 1. Features

- Supply voltage: 2.7V to 3.6V

- 2-wire serial interface I<sup>2</sup>C/SMBus compatible

- Low operating current

- $-\!\!\!-$  5  $\mu A$  (max) TS in Shutdown mode and EEPROM in Standby mode

- $-\!\!\!\!-$  200  $\mu A$  (max) TS being active and EEPROM in

### 1.1 The 2Kb SPD EEPROM Features

- Functionality identical to GT34C02 device

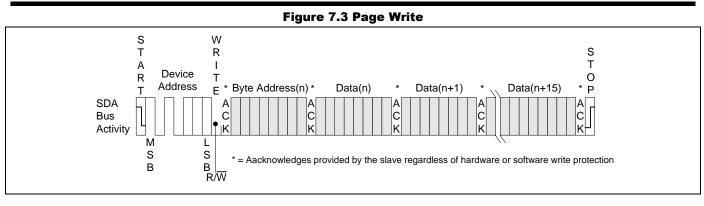

- Byte and Page Write Operations

- Page Size up to 16 bytes

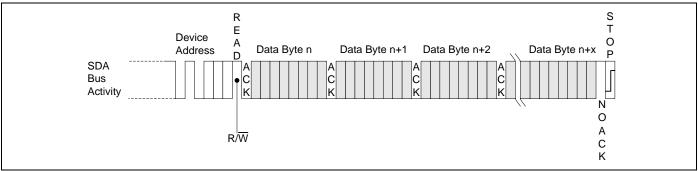

- Random and Sequential Read modes

- Self-Time Write Cycle (5ms, max)

- Automatic Address Incrementing

### **1.2 Temperature Sensor Features**

- Temperature sensor accuracy (Grade B):

- ±1°C from +70°C to +95°C

- ±2°C from +40°C to +125°C

- $-\!\!\! \pm 3^\circ C$  from -40°C to +125°C

- Temperature sensor resolution: 0.0625°C/LSB

- The TS continuously monitors the temperature and updates the temperature data typically ten times per second. Temperature data is latched internally by the

Standby mode

- 2 mA (max) TS in Shutdown and EEPROM are active

- Software Programmable Shutdown Mode

- Software reset feature

- Speed up to 400 kHz

- Permanent and Reversible Software data Protection for the lower 128 bytes

- Noise filter on bus inputs

- More than 1 million Erase/Write Endurance Cycles

- More than 40 years Data Retention

- Operating Temperature range: -40°C to +85°C

device and may be read by software from the bus host at any time.

- Temperature sampling (ADC conversion) time: 125 msec (max.)

- Hysteresis selectable set points from: 0, 1.5°C, 3°C & 6°C

- Ambient temperature sensing range: -40°C to +125°C

The GT34TS02 is a Temperature Sensor (TS) product with embedded 2K-bit Serial Presence Detect (SPD) EEPROM, which is fully compatible to industrial standard  $I^2C/SMB$ us interface and compliant to the JEDEC 42.4 specification. The EEPROM memory is organized as 256 x 8 bits and is functionally identical to the GT34C02. This product is designed for memory module applications in most PC and

### 2.1 2K-bit SPD EEPROM

The embedded 2K-bit serial SPD EEPROM has the functions identical to the GT34C02. One of the features is to permanently lock the data in its first half (lower) 128 bytes (address 00h to 7Fh). This feature is specifically designed for use in DRAM DIMM with SPD. All information concerning the DRAM module configuration (e.g. access speed, size, and organization) can be kept write-protected

#### **2.2 Temperature Sensor**

The TS monitors the ambient temperature ranging from -40°C to 125°C. The TS includes a high precision CMOS temperature sensor, a sigma-delta analog to digital converter (ADC) and a serial interface compatible to industrial standard I<sup>2</sup>C/SMBus. The ADC default resolution is set at 12-bit (0.0625°C). The accuracy over various temperature ranges is:

- ±1°C (max) for temperature range from +70°C to +95°C

- $\pm 2^{\circ}$ C (max) for temperature range from +40°C to +125°

- $\pm 3^{\circ}$ C (max) for temperature range from -40°C to 125°C

Server platforms, as well as other related applications. The unique GT34TS02 product operates from 2.7V to 3.6V and is offered in 8-pin Ultra-thin DFN package, 2 mm x 3 mm x 0.6 mm (max.), which is lead-free, RoHS, halogen free or Green compliance, providing space as well as cost saving for DIMM manufactures.

in the first half of the memory. The second half (upper) 128 bytes of the memory (address 80h to FFh) can't be write-protected using two different software write protection mechanisms. By sending a specified sequence to the device, the first 128 bytes memory can be write-protected either permanently or resettable. The operating ambient temperature ranging is from -40°C to +85°C.

The TS has shutdown current 5  $\mu$ A (max.) with SPD EE in Standby mode.

The TS component has user-programmable registers that provide the capabilities for DIMM temperature-sensing applications. The open drain  $\overline{\text{EVENT}}$  output pin is active when the monitoring temperature exceeds a programmable limit, or falls below or rises above an alarm window. The user has the option to set the  $\overline{\text{EVENT}}$  output as a critical temperature output. This output can be configured to operate in either a comparator mode for thermostat operation or in interrupt mode.

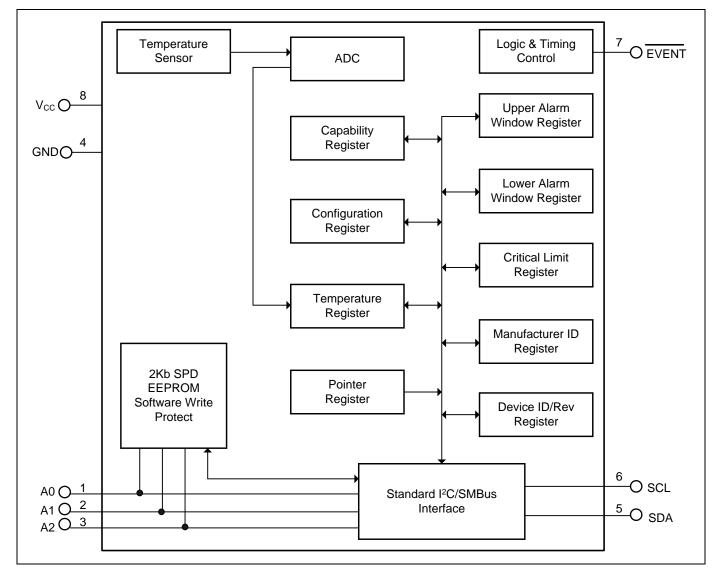

### **3. Functional Block Diagram**

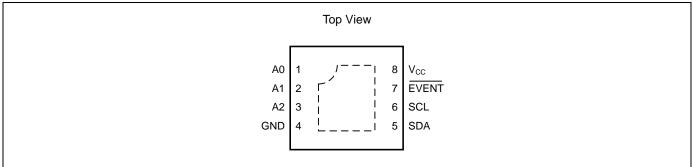

### 4. Pin Configuration

#### 4.1 8-Lead UDFN

#### 4.2 Pin Definition

| Pin No. | Pin Name        | I/O | Definition                                                  |

|---------|-----------------|-----|-------------------------------------------------------------|

| 1       | A0              | I   | Device Address Input                                        |

| 2       | A1              | I   | Device Address Input                                        |

| 3       | A2              | I   | Device Address Input                                        |

| 4       | GND             | -   | Ground                                                      |

| 5       | SDA             | I/O | Serial Address, Data input and Data output (Open drain)     |

| 6       | SCL             | I   | Serial Clock Input                                          |

| 7       | EVENT           | 0   | <b>EVENT</b> pin (open drain and active-low) <sup>[1]</sup> |

| 8       | V <sub>CC</sub> | -   | Power Supply                                                |

Note: <sup>[1]</sup> When active, functions as an Alert interrupt.

#### **4.3 Pin Descriptions**

#### SCL

This input clock pin is used to synchronize the data transfer to and from the device.

#### SDA

The SDA is a bi-directional pin used to transfer addresses and data into and out of the device. The SDA pin is an open drain output and can be wired with other open drain or open collector outputs. However, the SDA pin requires a pull-up resistor connected to the power supply.

#### A0, A1, A2

The A0, A1 and A2 are the device address inputs. Typically, the A0, A1, and A2 pins are for hardware addressing and a total of 8 devices can be connected on a single bus system. When A0, A1, and A2 are left floating, the inputs are defaulted to zero.

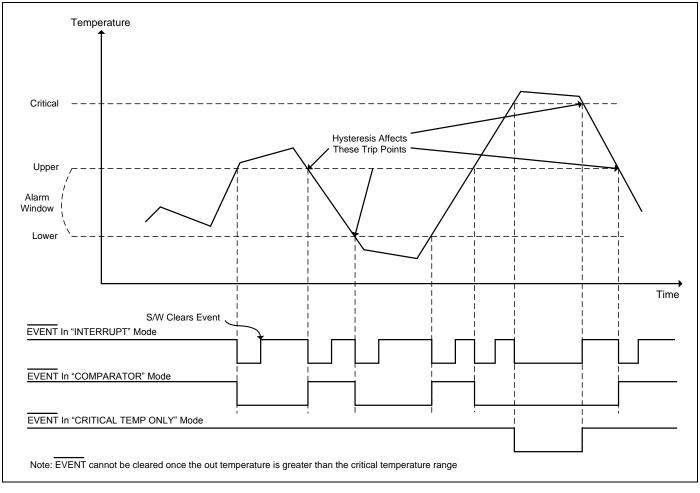

#### EVENT

The **EVENT** pin is an open-drain pin that can be defined by the configuration register. The **EVENT** output reacts to temperature changes as illustrated in Figure 6-2

#### Vcc

Supply voltage

#### GND

Ground of supply voltage

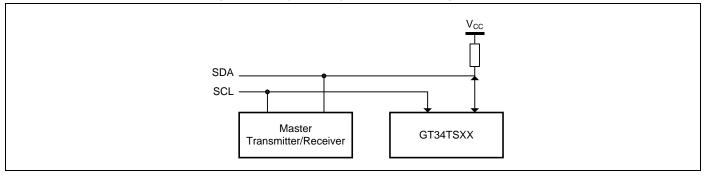

### 5. I<sup>2</sup>C / SMBus Serial Interface

#### 5.1 Serial bus interface

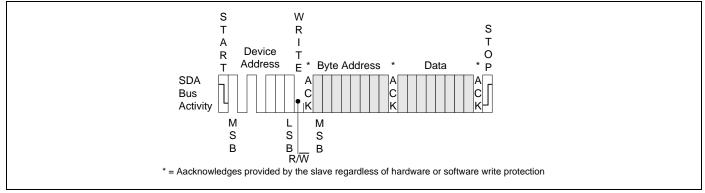

The GT34TS02 utilizes the industrial standard 2-wire bus supporting either  $I^2C$  or SMBus protocol to communicate with a master controller. The master generates the SCL signal and GT34TS02 being a slave device utilizes the SCL signal to receive or send data via the SDA line. Data transfer is serial, bi-directional, and is one bit at a time with the Most Significant Bit (MSB) transferred first, and a complete  $I^2C$  bus data is 1-byte. Since SDA and **EVENT** are open-drain, pull-up resistors are required.

#### 5.2 I<sup>2</sup>C / SMBus Communication

This protocol provides the communications to

- The registers selected by the Pointer register.

- At power-up, the Pointer register is set to "00", i.e. the Capability register location.

- The Pointer register latches the last location being set to. Also, pending upon the selected bits [P2:P0] of pointer register, each data registers falls into one of two types of user accessibility:

- Read only

- Write / Read

- A Write to GT34TS02 will always include the address byte and the pointer byte. A Write to any register other than the pointer register, requires two data bytes.

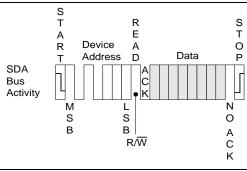

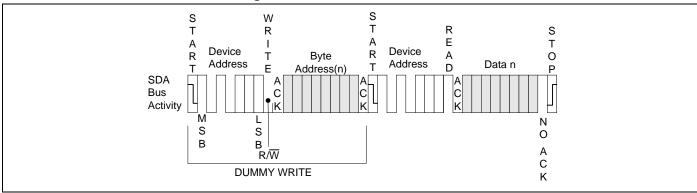

- A Read operation can be performed in either

- If the location latched in the Pointer register is correct (most of the time it is expected that the Pointer register will point to one of the Read Temperature registers because that will be the data most frequently read), then the Read can simply consist of an address byte, followed by retrieval of the two data bytes, OR

- If the Pointer register needs to be set, then an address byte, pointer byte, repeat start, and another address byte will accomplish a Read

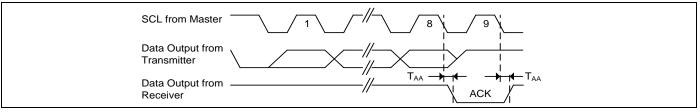

- The data byte communication transfers the MSB (Bit 7) first.

- At the end of a Read, GT34TS02 can accept either an

Acknowledge (ACK) or No Acknowledge (No ACK) status from the Master. The No ACK status is typically used as a signal for the slave that the Master has read its last byte. This device subsequently takes up to 125ms to measure the temperature.

For the SMBus communication, conditions of 10KHz minimum clock frequency, 300ns data hold time and 50ms maximum time-out (TS only) are required.

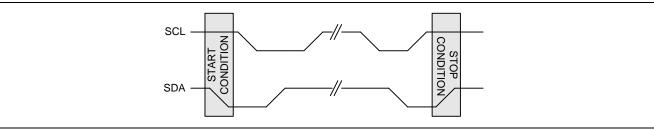

#### **5.3 Start Condition**

The Start condition precedes all commands to the device and is defined as a High to Low transition of SDA when SCL is High. The EEPROM monitors the SDA and SCL lines and will not respond until the Start condition is met.

#### 5.4 Stop Condition

The Stop condition is defined as a Low to High transition of SDA when SCL is High. All operations must end with a Stop condition.

#### 5.5 Acknowledge

After a successful data transfer, each receiving device is required to generate an ACK. The Acknowledging device pulls down the SDA line.

#### 5.6 Slave address

GT34TS02 uses 7-bit slave address, which consists of 4 fixed bits (Device Type Identifier, D0~D3) and 3 programmable bits (A0, A1 and A2), allowing a total of eight devices to co-exist on the same bus. The input of each pin is sampled at the start of each I<sup>2</sup>C/SMBus access.

The TS and EEPROM in GT34TS02 each have its own unique  $I^2C$  address for the 4 bits Device Type Identifier (DTI), which are the first 4 bits of the Slave address:

- 0011: TS

- 1010 : EE

- 0110:Access software write protection operations on the EEPROM

The rest of 3 bits, A2, A1 and A0, are configurable to select one of eight possible Slave devices.

The last bit,  $R/\overline{w}$ , specifies whether a Read (1) or Write (0) operation is being performed.

| Memory Area Function                    |                        | Slave Address |    |    |          |         |         |                |  |

|-----------------------------------------|------------------------|---------------|----|----|----------|---------|---------|----------------|--|

|                                         | Device Type Identifier |               |    |    | Select / | Address | Signals | <b>R</b> / w # |  |

|                                         | D3                     | D2            | D1 | DO | A2       | A1      | A0      |                |  |

| Read/Write TS Register                  | 0                      | 0             | 1  | 1  | A2       | A1      | A0      | R/ w #         |  |

| Read/Write EEPROM Memory                | 1                      | 0             | 1  | 0  | A2       | A1      | A0      | R/ w #         |  |

| Set Write Protection (SWP)              |                        |               |    |    | 0        | 0       | 1       | 0              |  |

| Clear Write Protection (CWP)            |                        |               |    |    | 0        | 1       | 1       | 0              |  |

| Permanently Set Write Protection (PSWP) | 0                      | 1             | 1  | 0  | A2       | A1      | A0      | 0              |  |

| Read SWP                                |                        |               |    |    | 0        | 0       | 1       | 1              |  |

| Read CWP                                |                        |               |    |    | 0        | 1       | 1       | 1              |  |

| Read PSWP                               |                        |               |    |    | A2       | A1      | A0      | 1              |  |

| Table | 5.1          | Device | Address  | Format   |

|-------|--------------|--------|----------|----------|

| Ianic | <b>J</b> . I | Device | Auui C33 | i vi mat |

Note: D3 (MSB), R/w # (LSB)

#### **5.7 Power-Up and Reset States**

GT34TS02

#### 5. 7.1 Power-Up Condition

After power-on, GT34TS02 is initialized to the following default condition:

- Pointer register is defaulted to 00h

- Starts monitoring local sensor

- EVENT register is cleared: EVENT output is pulled high by external pull-up resistor.

- EVENT hysteresis is defaulted to 0°C

- Critical temperature, Alarm Temperature Upper and Lower register are defaulted to 0°C

- Capability register is defaulted to 001Fh

- Operational mode: comparator

After supply voltage reaches to a stable minimum level, TS needs a minimum of 250 msec prior to perform an appropriate measurement.

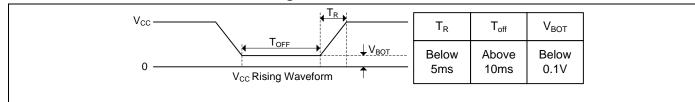

The device incorporates a power on reset circuit, which protects the internal logic against powering up into a wrong state. Nevertheless, the following conditions on power supply are recommended in the Figure 5.1.

#### 5. 7.2 Software Reset

The device contains a reset function in case the 2-wire bus transmission on is accidentally interrupted (e.g. a power loss), or needs to be terminated mid-stream. The reset is initiated when the Master device creates a Start condition. To do this, it may be necessary for the Master device to monitor the SDA line while cycling the SCL up to nine times. (For each clock signal transition to High, the Master checks for a High level on SDA.)

#### Figure 5.1 POR Condition

#### Figure 5-2. Typical System Bus Configuration

Figure 5-3. Start and Stop Conditions

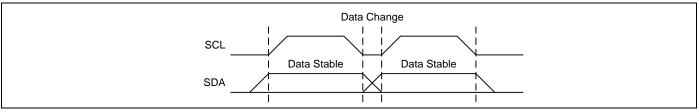

#### Figure 5-4. Data Validity Protocol

GT34TS02

### 6. Temperature Sensor

#### 6.1 TS Register Overview

The TS component in GT34TS02 includes various types of user-programmable registers. Their definitions and functions are described in the following sections.

The major registers are:

- Pointer register

- Capability register

- Configuration register

- Upper Alarm Window register

- Lower Alarm Window register

- Critical Limit register

- Temperature register

- Manufacturer ID register

- Device ID/Revision register

| Register Address | R/w                       | Default state | TS Register                   |

|------------------|---------------------------|---------------|-------------------------------|

| N/A              | W                         | N/A           | Pointer register              |

| 00h              | R                         | 001Fh         | Capability register (B-grade) |

| 01h              | $R/\overline{\mathbf{w}}$ | 0000h         | Configuration register        |

| 02h              | $R/\overline{\mathbf{w}}$ | 0000h         | Upper Alarm Window register   |

| 03h              | $R/\overline{\mathbf{w}}$ | 0000h         | Lower Alarm Window register   |

| 04h              | $R/\overline{\mathbf{w}}$ | 0000h         | Critical Limit register       |

| 05h              | R                         | N/A           | Temperature register          |

| 06h              | R                         | 132Dh         | Manufacturer ID register      |

| 07h              | R                         | 3300h         | Device ID/Revision register   |

Note: Any illegal operations or write to invalid/reserved registers is prohibited.

#### 6.1.1 Pointer Register

This register is an 8-bit register, which contains 3 selected

bits: P0, P1 and P2.

#### Table 6.2 Pointer Register Format

| MSB   | Pointer register |       |       |       |       |       |       |  |

|-------|------------------|-------|-------|-------|-------|-------|-------|--|

| Bit 7 | Bit 6            | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

| 0     | 0                | 0     | 0     | 0     | P2    | P1    | P0    |  |

Note: P2, P1 and P0 are selected bits of pointer register.

| Table 6.3 Pointer | <sup>,</sup> Register | Description |

|-------------------|-----------------------|-------------|

|-------------------|-----------------------|-------------|

| P2 | P1 | PO | Name     | Description          | R/W | Default |

|----|----|----|----------|----------------------|-----|---------|

| 0  | 0  | 0  | TSCap    | TS capability        | R   | 001F    |

| 0  | 0  | 1  | Conf     | Configuration        | R∕₩ | 0000    |

| 0  | 1  | 0  | Upper    | Upper Alarm Window   | R∕₩ | 0400    |

| 0  | 1  | 1  | Lower    | Lower Alarm Window   | R/₩ | 00A0    |

| 1  | 0  | 0  | Critical | Critical Limit       | R∕₩ | 0500    |

| 1  | 0  | 1  | Temp     | Temperature          | R   | 0000    |

| 1  | 1  | 0  | MID      | Manufacturer ID      | R   | 132Dh   |

| 1  | 1  | 1  | DID      | Device ID / Revision | R   | 3300h   |

#### 6.1.2 Capability Register

This register is a 16-bit register with default value 001Fh

| MSB   |       |       | LSB                    |       |       |          |                        |  |  |  |

|-------|-------|-------|------------------------|-------|-------|----------|------------------------|--|--|--|

| Bit15 | Bit14 | Bit13 | Bit12                  | Bit11 | Bit10 | Bit9     | Bit8                   |  |  |  |

| RFU   | RFU   | RFU   | RFU                    | RFU   | RFU   | RFU      | RFU                    |  |  |  |

| 0     | 0     | 0     | 0                      | 0     | 0     | 0        | 0                      |  |  |  |

| Bit7  | Bit6  | Bit5  | Bit4                   | Bit3  | Bit2  | Bit1     | Bit0                   |  |  |  |

| RFU   | RFU   | RFU   | Temperature resolution |       | Range | Accuracy | Alarm & Critical Trips |  |  |  |

| 0     | 0     | 0     | 1                      | 1     | 1     | 1        | 1                      |  |  |  |

#### **Table 6.4 Capability Register Format**

#### **Table 6.5 Capability Register Description**

| Bit  | Symbol                 | R/W | Description                                                                                                |

|------|------------------------|-----|------------------------------------------------------------------------------------------------------------|

| 0    | Alarm & Critical Trips | R   | Basic capability.                                                                                          |

|      |                        |     | 0: The device does not support interrupt capabilities.                                                     |

|      |                        |     | 1 (Default): Has Alarm and Critical Trips capability                                                       |

| 1    | Accuracy               | R   | Higher accuracy bit set during manufacture.                                                                |

|      |                        |     | 0: Accuracy ±2°C over the active range and ±3°C over the monitor range (C-grade)                           |

|      |                        |     | 1 (Default): Accuracy $\pm 1^{\circ}$ C over the active range and $\pm 2^{\circ}$ C over the monitor range |

|      |                        |     | (B-grade)                                                                                                  |

| 2    | Range                  | R   | 0: The temperature monitor clamps values lower than 0°C.                                                   |

|      |                        |     | 1 (Default): can be read temperatures below 0°C and set sign bit accordingly                               |

| 4:3  | Temperature            | R   | Temperature resolution                                                                                     |

|      | resolution             |     | 11 (Default): This 12-bit setting provides temperature at 0.0625°C resolution (LSB)                        |

| 15:5 | RFU                    | R   | Reserved for future use. Must be Zero                                                                      |

#### 6.1.3 Configuration Register

This register is a 16-bit register with default value 0000h

| MSB           |            |       | LSB    |         |            |          |             |

|---------------|------------|-------|--------|---------|------------|----------|-------------|

| Bit15         | Bit14      | Bit13 | Bit12  | Bit11   | Bit10      | Bit9     | Bit8        |

| RFU           | RFU        | RFU   | RFU    | RFU     | Hysteresis |          | Shutdown TS |

| 0             | 0          | 0     | 0      | 0       | 0          | 0        | 0           |

| Bit7          | Bit6       | Bit5  | Bit4   | Bit3    | Bit2       | Bit1     | Bit0        |

| Critical Lock | EVENT Lock | Clear | EVENT  | EVENT   | Critical   | EVENT    | EVENT Mode  |

|               |            |       | Status | Control | Event      | Polarity |             |

| 0             | 0          | 0     | 0      | 0       | 0          | 0        | 0           |

|                  |               |                  | Table 6.7 Configuration Register Description                                                                                         |

|------------------|---------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Bit              | Parameter     | <b>R</b> / w     | Description                                                                                                                          |

| 0                | EVENT         | R/₩              | 0: Comparator output mode (Default)                                                                                                  |

|                  | Mode          |                  | 1: Interrupt mode                                                                                                                    |

|                  |               |                  | • When either of the Alarm (6) or Critical (7) lock bit is set, this bit cannot be altered until                                     |

|                  |               |                  | unlocked                                                                                                                             |

| 1                | EVENT         | R/₩              | 0: Low (Default)                                                                                                                     |

|                  | Polarity      |                  | 1: HIGH.                                                                                                                             |

|                  |               |                  | • When either of the Alarm (6) or Critical (7) lock bit is set, this bit cannot be altered until unlocked.                           |

| 2                | Critical      | R/₩              | 0: <b>EVENT</b> output on Alarm or Critical temperature event (Default)                                                              |

|                  | EVENT         |                  | 1: <b>EVENT</b> only if temperature is above the value in the critical temperature register                                          |

|                  |               |                  | • When the alarm window lock bit (6) is set, this bit cannot be altered until unlocked.                                              |

| 3                | EVENT         | $R/\overline{W}$ | 0: <b>EVENT</b> output disabled (Default)                                                                                            |

|                  | Control       |                  | 1: EVENT output enabled                                                                                                              |

|                  |               |                  | • When either of the lock bits (6 or 7) is set, this bit cannot be altered until unlocked.                                           |

| 4                | EVENT         | R                | 0: Not assert <b>EVENT</b> output condition (Default)                                                                                |

|                  | Status        |                  | 1: Assert <b>EVENT</b> output condition due to Alarm Window or Critical Trip condition.                                              |

|                  |               |                  | • The actual event causing the event can be determined from the Read Temperature                                                     |

|                  |               |                  | register. Interrupt <b>EVENT</b> can be cleared by writing to the 'clear <b>EVENT</b> ' bit. Writing to this bit will have no effect |

| 5                | Clear         | W                | Clear EVENT                                                                                                                          |

|                  |               |                  | 0: No-effect (Default)                                                                                                               |

|                  |               |                  | 1: Clears active <b>EVENT</b> in Interrupt mode.                                                                                     |

|                  |               |                  | When read, this register always returns zero.                                                                                        |

|                  |               |                  | Writing to this register has no effect in Comparator mode.                                                                           |

| 6                | EVENT         | R/₩              | Alarm Window Lock bit                                                                                                                |

|                  | Lock          |                  | 0: Upper and Lower Alarm Window registers are unlocked and can be altered (Default).                                                 |

|                  |               |                  | 1: Upper and Lower Alarm Window registers are locked and setting cannot be altered.                                                  |

|                  |               |                  | • Once power-up, this bit is initially cleared. When set, this bit will return a 1 and remains                                       |

|                  |               |                  | locked until cleared by internal power-on reset                                                                                      |

|                  |               |                  | This bit can be written with a single write and does not require double writes                                                       |

| 7                | Critical Lock | $R/\overline{W}$ | Critical Lock bit                                                                                                                    |

|                  |               |                  | 0: Critical Limit register is unlocked and can be altered (Default)                                                                  |

|                  |               |                  | 1: Critical Limit register settings is locked and cannot be changed.                                                                 |

|                  |               |                  | • Once power-up, this bit is initially cleared. When set, this bit becomes a 1, and remains                                          |

|                  |               |                  | locked until cleared by internal Power-on reset                                                                                      |

|                  |               |                  | This bit can be written with a single write and do not require double writes.                                                        |

| 8 <sup>[1]</sup> | Shutdown TS   | $R/\overline{W}$ | 0: Enable TS (Default)                                                                                                               |

|                  |               |                  | 1: Disable TS                                                                                                                        |

| Bit   | Parameter  | R/w | Description                                                                                      |

|-------|------------|-----|--------------------------------------------------------------------------------------------------|

|       |            |     | • When disabled, entire TS component is shut down and enter into standby mode to save            |

|       |            |     | power, no events will be generated. However, all registers may be read or written to.            |

|       |            |     | • When either of the lock bits (6 or 7) is set, this bit cannot be set to 1 until they are       |

|       |            |     | unlocked.                                                                                        |

|       |            |     | • However, this bit can be cleared to 0 at any time. Also, power cycling will clear this bit and |

|       |            |     | enable the TS to active mode.                                                                    |

| 10:9  | Hysteresis | R/₩ | 00: Disable hysteresis (Default)                                                                 |

|       |            |     | 01: Enable hysteresis at 1.5°C                                                                   |

|       |            |     | 10: Enable hysteresis at 3°C                                                                     |

|       |            |     | 11: Enable hysteresis at 6°C                                                                     |

|       |            |     | • When enabled, hysteresis is applied to temperature movement around trigger points.             |

|       |            |     | Refer to Hysteresis section below for details.                                                   |

| 15:11 | RFU        | R   | Reserved for future use. Must be Zero                                                            |

Note: <sup>[1]</sup> If either Bit 6 or Bit 7 is set, then this bit can't be set until they are unlocked.

#### 6.1.3.1 Hysteresis

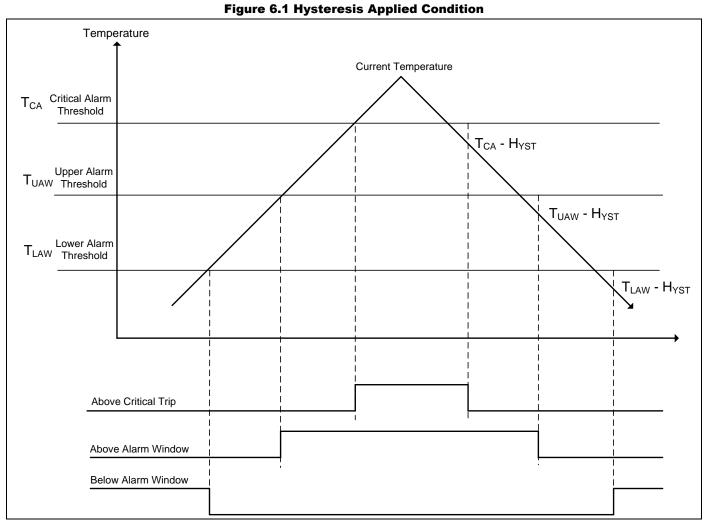

Hysteresis is applied in the following conditions like the Table 6.7, Table 6.8 and Figure 6-1.

- For example, consider the behavior of the 'Above Alarm Window' bit (Bit14) of the Temperature register with the hysteresis being set to 3 °C setting. As the ambient temperature rises and exceeds the alarm window, (i.e., when the Temperature register contains a value that is greater than the value of the Upper Alarm Window register), then Bit14 will be set to 1. If the ambient temperature decreases, Bit14 will remain set unless the measured temperature is less than or equal to 3°C below the value in the Upper Alarm Window register

- Similarly, the 'Below Alarm Window' bit (Bit13) of the Temperature register will be set to 0 when the value in the Temperature register is equal to or greater than the value in the Lower Alarm Window register. However, once the temperature decreases to less than the value in the Lower Alarm Window register minus 3°C, Bit13 will be set to 1.

- Note that hysteresis is also applied to EVENT pin functionality. When either of the lock bits (6 & 7) is set, these bits cannot be altered.

|        | Below Ala         | rm window bit                              | Above Ala         | rm window bit                              |

|--------|-------------------|--------------------------------------------|-------------------|--------------------------------------------|

|        | Temperature slope | Threshold temperature                      | Temperature slope | Threshold temperature                      |

| Sets   | Falling           | T <sub>LAW</sub> - <b>H</b> <sub>YST</sub> | Rising            | T <sub>UAW</sub>                           |

| Clears | Rising            | T <sub>LAW</sub>                           | Falling           | T <sub>UAW</sub> - <b>H</b> <sub>YST</sub> |

#### **Table 6.8 Hysteresis Applied Condition**

Note:  $T_{UAW}$  = Upper Alarm Window value;  $T_{LAW}$  = Lower Alarm Window value;  $H_{YST}$  = Absolute value of selected hysteresis;  $T_{CA}$  = Critical Alarm value

#### **6.1.4 Temperature Register**

This register is a 16-bit register holding the temperature value

The data of this register can be read at any time • without interrupting the temperature conversion process

- The LSB (0) equals to 0.0625°C

- Bits 13 to 15 are limit setting bits

| Table 6.9 | Temperature | Register | Description |

|-----------|-------------|----------|-------------|

|           | remperature | Negister | Description |

| Bit  | Symbol | Access | Description                                          |

|------|--------|--------|------------------------------------------------------|

| 12:0 | TEMP   | R      | Temperature Value (2's complement). (LSB = 0.0625°C) |

|          |                      |          | MSB   |       |       |      |      |        |          |      |      |      |      |      | LSB  |

|----------|----------------------|----------|-------|-------|-------|------|------|--------|----------|------|------|------|------|------|------|

| Bit15[*] | Bit14 <sup>[*]</sup> | Bit13[*] | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | Bit7   | Bit6     | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| Above    | Above                | Below    |       |       |       |      |      |        |          |      |      |      |      |      |      |

| Critical | Alarm                | Alarm    | Sign  |       |       |      | Т    | empera | ature va | alue |      |      |      |      | 0    |

| Alarm    | Window               | Window   |       |       |       |      |      |        |          |      |      |      |      |      |      |

|       | Table 6.11 Bit[15], Bit[14], Bit[13] Description                                                                      |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| Bit # | Definition with Hysteresis = 0                                                                                        |

| 13    | Below Alarm Window                                                                                                    |

|       | 0 : temperature is equal to or above the Lower Alarm Window register                                                  |

|       | • 1 : temperature is below the Lower Alarm Window register                                                            |

|       | When the temperature is below the Lower Alarm Window value, this bit is set and will remain set as long as the        |

|       | temperature is below the Lower Limit minus the hysteresis. When the temperature meets or exceeds the Lower            |

|       | Limit, it will only be cleared.                                                                                       |

| 14    | Above Alarm Window                                                                                                    |

|       | 0 : temperature is equal to or below the Upper Alarm Window register                                                  |

|       | 1 : temperature is above Upper Alarm Window register                                                                  |

|       | When the temperature is above the Upper Alarm Window value, this bit is set and will remain set as long as the        |

|       | temperature is above the Upper value. Once when the temperature drops below or equal to the Upper value minus         |

|       | the hysteresis, it will be cleared.                                                                                   |

| 15    | Above Critical Alarm                                                                                                  |

|       | 0 : temperature is below the Critical Alarm register setting                                                          |

|       | • 1 : temperature is equal to or above the Critical Alarm register setting                                            |

|       | When the temperature is above the Critical Alarm, this bit is set and will remain set as long as the temperature is   |

|       | above Critical Alarm. Once the temperature has dropped below the limit minus the hysteresis, it will automatically be |

|       | cleared.                                                                                                              |

#### 6.1.5 Upper Alarm Window Register

This register is a 16-bit register holding the Upper Alarm Window temperature value

LSB equals to 0.25°C

#### **Table 6.12 Upper Alarm Window Register Format**

|       |       |       | MSB   |       |       |      |          |        |         |           |       |      | LSB  |      |      |

|-------|-------|-------|-------|-------|-------|------|----------|--------|---------|-----------|-------|------|------|------|------|

| Bit15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8     | Bit7   | Bit6    | Bit5      | Bit4  | Bit3 | Bit2 | Bit1 | Bit0 |

| 0     | 0     | 0     | Sign  |       |       | Upp  | er Alarm | Window | v Tempe | erature v | value |      |      | 0    | 0    |

#### 6.1.6 Lower Alarm Window Register

This register is a 16-bit register holding the Lower Alarm

LSB equals to 0.25°C •

Window temperature value

|       |       |       | MSB   |       |       |      |          |         |        |         |       |      | LSB  |      |      |

|-------|-------|-------|-------|-------|-------|------|----------|---------|--------|---------|-------|------|------|------|------|

| Bit15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8     | Bit7    | Bit6   | Bit5    | Bit4  | Bit3 | Bit2 | Bit1 | Bit0 |

| 0     | 0     | 0     | Sign  |       |       | Low  | er Alarm | n Windo | w Temp | erature | value |      |      | 0    | 0    |

#### **Table 6.13 Lower Alarm Window Register Format**

#### 6.1.7 Critical Alarm Register

This register is a 16-bit register holding the Critical Alarm temperature value

LSB equals to 0.25°C

| _     |       |       |       | Iar   | DIE 6.14 | 4 Critic | cai Aia    | rm ke    | gister  | Forma    | τ    |      |      |      |      |

|-------|-------|-------|-------|-------|----------|----------|------------|----------|---------|----------|------|------|------|------|------|

|       |       |       | MSB   |       |          |          |            |          |         |          |      |      | LSB  |      |      |

| Bit15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10    | Bit9     | Bit8       | Bit7     | Bit6    | Bit5     | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 0     | 0     | 0     | Sign  |       |          |          | Critical A | Alarm Te | mperate | ure valu | е    |      |      | 0    | 0    |

#### 6.1.8 Manufacturer's ID Register

This register is a 16-bit register for Manufacturer ID (132Dh)

#### 6.1.9 Device ID Register

This register is a 16-bit register for Device ID (3300h)

• The upper byte stores a unique number Device ID.

#### 6.2 EVENT output

The **EVENT** pin is an open-drain output whose function can be programmed as an interrupt, comparator, or critical alarm mode.

#### 6.2.1 Interrupt Mode

When the temperature exceeds the value in either the Upper or Lower Alarm Window register, the device will trigger the  $\overrightarrow{\text{EVENT}}$  interrupt. By writing a "1" to the Clear  $\overrightarrow{\text{EVENT}}$  Bit[5] of Configuration Register will clear the status.

#### **6.2.2 Comparator Mode**

The **EVENT** pin remains asserted until the temperature falls below the value programmed in the Upper Alarm Window register or rises above the value programmed in the Lower Alarm Window register, or until the range of these alarm registers are reprogrammed and the temperature falls inside the Alarm limits.

#### 6.2.3 Critical Mode

When the temperature reaches beyond a critical temperature, the device switches to the comparator mode automatically and triggers the  $\overline{EVENT}$  interrupt. Such state will remain as long as the temperature stays above the

• The lower byte holds the revision value.

critical setting. Under such condition, the **EVENT** Status cannot be cleared through the clear **EVENT** bit or SMBus Alert.

When the temperature drops below critical temperature, the

**EVENT** output can be only cleared and the device reverts back to either interrupt or comparator mode, pending upon the programmed status of Bit 0 (**EVENT** mode) in the Configuration register. Or performing the SMBus Alert

Response address (ARA), if SMBus is utilized.

All event thresholds use hysteresis as programmed in the Configuration register.

#### 6.3 Alarm window

The alarm window consists of two registers: an Upper Alarm Window register (02h) and a Lower Alarm Window register (03h). The Upper Alarm Window register holds the upper temperature point, while the Lower Alarm Window register holds the lower temperature point. When the **EVENT** control is enabling, the **EVENT** output will be triggered whenever entering or exiting the alarm window.

#### Figure 6.2 Hysteresis Applied Condition

GT34TS02

### 7. EEPROM Functional Description

#### 7.1 Read and Write Operation

For EE, all functions on Read, Write, software protections and others are the same as GT34C02, which includes byte write, page write, random access read, current address read, sequential read, SWP, CWP and PSWP.

| Pin C | Connect         | ion <sup>[1]</sup> |     | Slave I    | Device | Addres | s |    |          |    |     |                                                          |

|-------|-----------------|--------------------|-----|------------|--------|--------|---|----|----------|----|-----|----------------------------------------------------------|

| A2    | A1              | A0                 | Bit | 7          | 6      | 5      | 4 | 3  | 2        | 1  | 0   |                                                          |

| A2    | A1              | A0                 |     | 1          | 0      | 1      | 0 | A2 | A1       | A0 | R/W | Normal<br>Instruction <sup>[2]</sup>                     |

| A2    | A1              | A0                 |     | 0          | 1      | 1      | 0 | A2 | A1       | A0 | R/W | Permanent Write<br>Protection Instruction <sup>[2]</sup> |

| GND   | GND             | V <sub>HV</sub>    |     | 0          | 1      | 1      | 0 | 0  | 0        | 1  | 0   | Set Write Protection (SWP)                               |

| GND   | V <sub>CC</sub> | V <sub>HV</sub>    |     | 0          | 1      | 1      | 0 | 0  | 1        | 1  | 0   | Clear Write Protection (CWP)                             |

| GND   | GND             | V <sub>HV</sub>    |     | 0          | 1      | 1      | 0 | 0  | 0        | 1  | 1   | Read SWP                                                 |

| GND   | V <sub>cc</sub> | V <sub>HV</sub>    |     | 0          | 1      | 1      | 0 | 0  | 1        | 1  | 1   | Read CWP                                                 |

|       | -               | -                  |     | ns must be | -      |        |   |    | the evte |    |     |                                                          |

### Figure 7.1 Command Configuration

#### Figure 7.4 Current Address Read

#### Figure 7.5 Random Address Read

Figure 7.6 Sequential Read

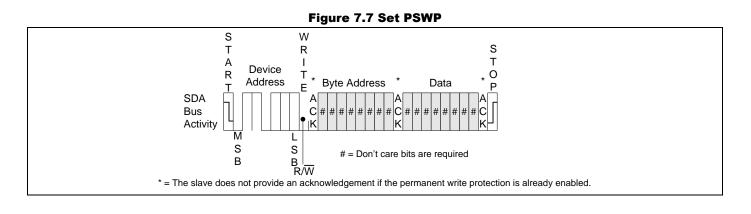

#### 7.2 Write Protection

#### 7.2.1 Software Write Protection

The EEPROM has two software write-protection features, allowing the lower half of the memory area (addresses 0x00 to 0x7F) to be temporarily or permanently write protected. Software write-protection is handled by three instructions:

- SWP: Set Write Protection

- CWP: Clear Write Protection

- PSWP: Permanently Set Write Protection

The level of write-protection (set or cleared) that has been defined using these instructions, remains defined even after a power cycle.

#### 7.2.2 SWP and CWP

If the software write-protection has been set with the SWP instruction, it can be cleared again with a CWP instruction. The two instructions (SWP and CWP) have the same format as a Byte Write instruction, but with a different Device Type Identifier. Like the Byte Write instruction, it is followed by an address byte and a data byte, but in this case the contents are all "Don't Care". Another difference is that the voltage,  $V_{HV}$  must be applied on the A0 pin, and specific logical levels must be applied on the other two A1 pin and A2 pin.

#### 7.2.3 PSWP

If the software write-protection has been set with the PSWP instruction, the first 128 bytes of the memory are permanently write-protected. This write-protection cannot be cleared by any instruction, or by power-cycling the

device. Also, once the PSWP instruction has been successfully executed, the SPD EE no longer acknowledges any instruction (with a Device Type Identifier of 0110) to access the write-protection settings. The slave respond with ACK or No ACK depends on the flag status (See Table 7.1)

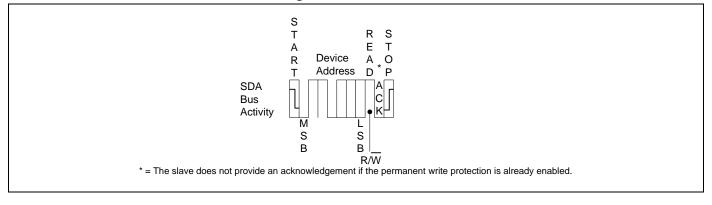

#### 7.3 Reading Write Protection Status

The status of software write protection can be determined using these instructions:

- Read SWP: Read Write Protection Status

- Read PSWP: Read Permanently Set Write Protection Status

#### 7.3.1 Read SWP

The host issues a Read SWP command. If Software Write Protection has not been set, the device replies to the data byte with an Ack. If Software Write Protection has been set, the device replies to the data byte with a NoAck (See Table 7.1).

#### 7.3.2 Read PSWP

The host issues a Read PSWP command. If Permanent Software Write Protection has not been set, the device replies to the data byte with an Ack. If Permanent Software Write Protection has been set, the device replies to the data byte with a NoAck (See Table 7.1).

Figure 7.8 Read PSWP

| Table 7.1 ACK Status             |                     |                      |                |                  |                |            |                  |                |  |

|----------------------------------|---------------------|----------------------|----------------|------------------|----------------|------------|------------------|----------------|--|

| Normal Instructions              |                     |                      |                |                  |                |            |                  |                |  |

| Command                          | PSWP<br>(Permanent) | RSWP<br>(Reversible) | ACK<br>command | Address          | ACK<br>Address | Data Byte  | Data Byte<br>ACK | Write<br>Cycle |  |

| Read                             | Х                   | Х                    | ACK            | 00h-FFh          | ACK            | Data Byte  | ACK              | No             |  |

| Write                            | 0                   | 0                    | ACK            | 00h-FFh          | ACK            | Data Byte  | ACK              | Yes            |  |

| Write                            | 1                   | Х                    | ACK            | 00h-7Fh          | ACK            | Data Byte  | NoACK            | No             |  |

| Write                            | Х                   | 1                    | ACK            | 00h-7Fh          | ACK            | Data Byte  | NoACK            | No             |  |

| Write                            | Х                   | Х                    | ACK            | 80h-FFh          | ACK            | Data Byte  | ACK              | Yes            |  |

|                                  |                     | Реі                  | rmanent In     | structions       | ;              |            |                  |                |  |

| Command                          | PSWP<br>(Permanent) | RSWP<br>(Reversible) | ACK<br>command | Address          | ACK<br>Address | Data Byte  | Data Byte<br>ACK | Write<br>Cycle |  |

| Read PSWP Status <sup>[3]</sup>  | 0                   | Х                    | ACK            | Dummy<br>Address | NoACK          | Dummy Byte | NoACK            | No             |  |

| Read PSWP Status                 | 1                   | Х                    | NoACK          | -                | -              | -          | -                | No             |  |

| Set PSWP                         | 0                   | Х                    | ACK            | Dummy<br>Address | ACK            | Dummy Byte | ACK              | Yes            |  |

| Set PSWP                         | 1                   | Х                    | NoACK          | -                | -              | -          | -                | No             |  |

|                                  |                     | Re                   | versible In    | structions       |                |            |                  |                |  |

| Command                          | PSWP<br>(Permanent) | RSWP<br>(Reversible) | ACK<br>command | Address          | ACK<br>Address | Data Byte  | Data Byte<br>ACK | Write<br>Cycle |  |

| Read SWP Status <sup>[3]</sup>   | 0                   | 0                    | ACK            | -                | -              | -          | -                | No             |  |

| Read SWP Status                  | 0                   | 1                    | NoACK          | -                | -              | -          | -                | No             |  |

| Read SWP Status <sup>[3]</sup>   | 1                   | 0                    | NoACK          | -                | -              | -          | -                | No             |  |

| Read SWP Status                  | 1                   | 1                    | NoACK          | -                | -              | -          | -                | No             |  |

| Read CWP status <sup>[2,3]</sup> | 0                   | Х                    | ACK            | -                | -              | -          | -                | No             |  |

| Read CWP status <sup>[2]</sup>   | 1                   | Х                    | NoACK          | -                | -              | -          | -                | No             |  |

| Set RSWP                         | 0                   | 0                    | ACK            | Dummy<br>Address | ACK            | Dummy Byte | ACK              | Yes            |  |

| Set RSWP                         | 0                   | 1                    | NoACK          | -                | -              | -          | -                | No             |  |

| Set RSWP                         | 1                   | 0                    | NoACK          | -                | -              | -          | -                | No             |  |

| Set RSWP                         | 1                   | 1                    | NoACK          | -                | -              | -          | -                | No             |  |

| Clear RSWP                       | 0                   | 0                    | ACK            | Dummy<br>Address | ACK            | Dummy Byte | ACK              | Yes            |  |

| Clear RSWP                       | 1                   | 0                    | NoACK          | -                | -              | -          | -                | No             |  |

| Clear RSWP                       | 0                   | 1                    | ACK            | Dummy<br>Address | ACK            | Dummy Byte | ACK              | Yes            |  |

| Clear RSWP                       | 1                   | 1                    | NoACK          | -                | -              | -          | -                | No             |  |

Note:<sup>[1]</sup> X = Don't care

$^{\mbox{\tiny [2]}}$  Read CWP status yields the same result as Read PSWP Status

<sup>[3]</sup> Read out Don't Care Dummy Address and Dummy Data is optional

### 8. Electrical Characteristics

#### 8.1 Absolute Maximum Ratings

| Symbol              | Parameter                               | Value         | Unit |

|---------------------|-----------------------------------------|---------------|------|

| V <sub>CC</sub>     | Supply Voltage                          | -0.3 to + 4.2 | V    |

| V <sub>N</sub>      | Voltage on SDA, SCL and EVENT Pins      | -0.3 to + 4.2 | V    |

| V <sub>A0</sub>     | Voltage on pin A0                       | -0.3 to +10   | V    |

| l <sub>sink</sub>   | Sink Current on SDA, SCL and EVENT Pins | -1 to +12.0   | mA   |

| T <sub>J(max)</sub> | Maximum Junction Temperature            | 150           | °C   |

| T <sub>stg</sub>    | Storage Temperature                     | -65 to +150   | °C   |

Note: Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### 8.2 Operating Range

| Range      | Ambient Temperature (T <sub>A</sub> ) | Vcc          |

|------------|---------------------------------------|--------------|

| Industrial | –40°C to +85°C                        | 2.7V to 3.6V |

Note: Giantec offers Industrial grade for Commercial applications (0°C to +70°C).

#### 8.3 Capacitance

| Symbol          | Parameter <sup>[1, 2]</sup> | Conditions     | Max. | Unit |  |

|-----------------|-----------------------------|----------------|------|------|--|

| C <sub>IN</sub> | Input Capacitance           | $V_{IN} = 0V$  | 6    | pF   |  |

| CI/O            | Input / Output Capacitance  | $V_{I/O} = 0V$ | 8    | pF   |  |

Notes: <sup>[1]</sup> Tested initially and after any design or process changes that may affect these parameters and not 100% tested.

<sup>[2]</sup> Test conditions:  $T_A = 25^{\circ}$ C, f = 1 MHz,  $V_{CC} = 2.7$ V to 3.6V, unless otherwise specified.

#### **8.4 DC Electrical Characteristic**

#### V<sub>cc</sub> = 2.7V to 3.6V, T<sub>amb</sub> = -40 °C to +85 °C, unless otherwise specified

| Symbol                                                                   | Parameter <sup>[1]</sup>                      | Conditions                                                   | Min.                 | Тур. | Max.                 | Unit   |

|--------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------|----------------------|------|----------------------|--------|

| V <sub>CC</sub>                                                          | Supply voltage                                |                                                              | 2.7                  | 3.3  | 3.6                  | V      |

| I <sub>LIH</sub> , I <sub>LIL</sub> ,I <sub>LOH</sub> , I <sub>LOL</sub> | Input/Output Leakage current                  | $V_{PIN}=V_{CC}$ or GND                                      |                      |      | ±4                   | μA     |

| I <sub>CC1</sub>                                                         | Operating current                             | TS active and EE standby                                     |                      |      | 200                  | uA     |

| I <sub>CC2</sub>                                                         | Operating current                             | TS shutdown and EE active                                    |                      |      | 2                    | mA     |

| I <sub>SD</sub>                                                          | Shutdown current                              | TS shutdown, EE standby<br>(I <sup>2</sup> C/SMBus inactive) |                      |      | 5                    | uA     |

| VIH                                                                      | Input High Voltage                            | SCL, SDA                                                     | 0.7* V <sub>CC</sub> |      | V <sub>CC</sub> +0.5 | V      |

| VIL                                                                      | Input Low Voltage                             | SCL, SDA                                                     | -0.5                 |      | 0.3* V <sub>CC</sub> | V      |

| V <sub>HV</sub>                                                          | A0 High Voltage                               | $V_{HV}$ - $V_{CC} \geq 4.8 V$                               | 7                    |      | 10                   | V      |

| V <sub>OL</sub>                                                          |                                               | I <sub>OL</sub> =2.1mA, 2.7V<=V <sub>CC</sub> <=3.6V         |                      |      | 0.4                  | V      |

|                                                                          | Output Low Voltage                            | I <sub>OL</sub> =0.7mA, V <sub>CC</sub> =2.7V                |                      |      | 0.2                  |        |

| $I_{OL}$ EVENT                                                           | Output Low Sink Current on EVENT              | V <sub>OL</sub> =0.4V                                        | 1                    |      |                      | mA     |

| I <sub>OL_SDA</sub>                                                      | Output Low Sink Current on SDA                | V <sub>OL</sub> =0.6V                                        | 6                    |      |                      | mA     |

|                                                                          |                                               | T <sub>amb</sub> = 70 °C to 95 °C                            |                      |      | ±1.0                 | °C     |

| TS <sub>Acc</sub>                                                        | Temperature sensor (TS) accuracy<br>(B-grade) | T <sub>amb</sub> = 40 °C to 125 °C                           |                      |      | ±2.0                 | °C     |

|                                                                          | (D-grade)                                     | T <sub>amb</sub> = -40 °C to 125 °C                          |                      |      | ±3.0                 | °C     |

| TS <sub>Res</sub>                                                        | TS Resolution                                 | 12-bit ADC                                                   |                      |      | 0.0625               | °C/LSB |

| R <sub>ADC</sub>                                                         | ADC Resolution                                |                                                              |                      |      | 12                   | Bits   |

| TS <sub>Conv</sub>                                                       | Conversion Rate                               |                                                              |                      |      | 125                  | ms     |

Notes: <sup>[1]</sup> Not all parameters are 100% tested.

This specification only indicates how often temperature information is updated to the Temperature Register.

Accuracy (express in °C) = difference between the output temperature and the measured temperature

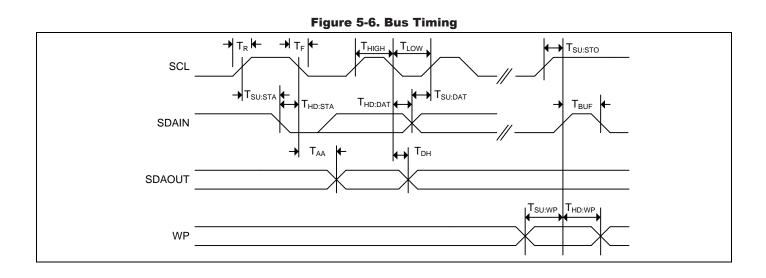

#### **8.5 AC Electrical Characteristic**

#### $V_{CC}$ = 2.7V to 3.6V, $T_{amb}$ = 25°C, unless otherwise specified

| Symbol                               | Parameter <sup>[1]</sup>                            | Min. | Тур. | Max. | Unit |

|--------------------------------------|-----------------------------------------------------|------|------|------|------|

| F <sub>SCL</sub>                     | SCL clock frequency                                 | 10   |      | 400  | kHz  |

| T <sub>LOW</sub>                     | Low period of SCL clock                             | 1300 |      |      | ns   |

| T <sub>HIGH</sub>                    | High period of SCL clock                            | 600  |      |      | ns   |

| T <sub>BUF</sub>                     | Bus free time between a Stop and a Start conditions | 1300 |      |      | ns   |

| T <sub>SU;STA</sub>                  | Start condition Setup time                          | 600  |      |      | ns   |

| T <sub>HD;STA</sub>                  | Start condition Hold time                           | 600  |      |      | ns   |

| T <sub>SU;STO</sub>                  | Stop condition Setup time                           | 600  |      |      | ns   |

| T <sub>SU;DAT</sub>                  | Data In Setup time                                  | 100  |      |      | ns   |

| T <sub>HD;DAT</sub> <sup>[2]</sup>   | Data In Hold time                                   | 0    |      |      | ns   |

| T <sub>DH</sub>                      | Data Out Hold Time                                  | 300  |      | 900  | ns   |

| T <sub>AA</sub>                      | SCL Low to SDA Data Out                             | 200  |      | 900  | ns   |

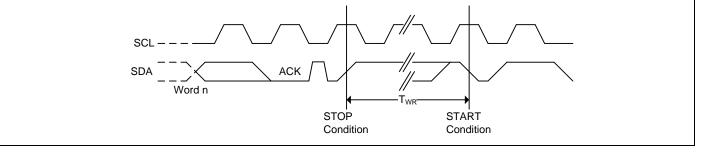

| T <sub>WR</sub>                      | Write Cycle                                         |      |      | 5    | ms   |

| T <sub>R</sub>                       | Rise time of SDA and SCL                            |      |      | 300  | ns   |

| T <sub>F</sub>                       | Fall time of SDA and SCL                            |      |      | 300  | ns   |

| Т                                    | Noise Suppression time                              |      |      | 100  | ns   |

| T <sub>PU</sub> <sup>[3]</sup>       | Power-up to temperature measurement                 | 250  |      |      | ms   |

| T <sub>time-out</sub> <sup>[4]</sup> | Bus time-out (TS only)                              | 20   |      | 50   | ms   |

Notes: <sup>[1]</sup> Not all parameters are 100% tested.

$^{\rm [2]}$  For the SMBus, 300 ns data in hold time,  $T_{\rm HD:DAT},$  is required.

<sup>[3]</sup> After V<sub>CC</sub> reaches the nominal value, 250msec is required prior to a valid temperature measurement

<sup>[4]</sup> The SMBus has a time-out of up to 50 ms for TS.

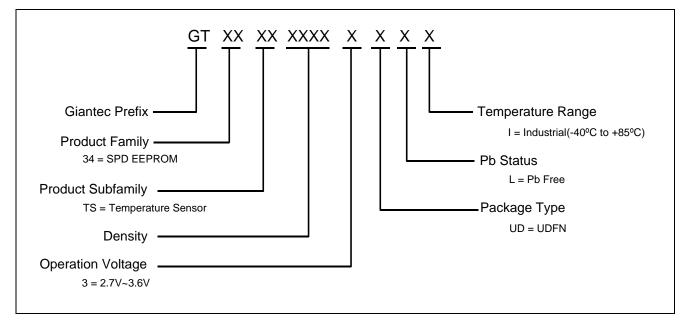

### 9. Ordering Information

#### Industrial Grade: -40°C to +85°C, Lead-free

| Voltage Range | Part Number*      | Package (8-pin)*               |

|---------------|-------------------|--------------------------------|

| 2.7V to 3.6V  | GT34TS02-3UDLI-TR | 2 x 3 x 0.55 mm Ultra-thin DFN |

\*

1. Contact Giantec Sales Representatives for availability and other package information.

2. The listed part numbers are packed in tape and reel "-TR". UDFN is 5K per reel.

3. Refer to Giantec website for related declaration document on lead free, RoHS, halogen free or Green, whichever is applicable.

4. Giantec offers Industrial grade for Commercial applications (0°C to +70°C).

### **10. Top Markings**

### 10.1 UDFN Package

*GT*: Giantec Logo <u>81</u>: GT34TS02-3UDLI-TR YWW: Date Code, Y=year, WW=week

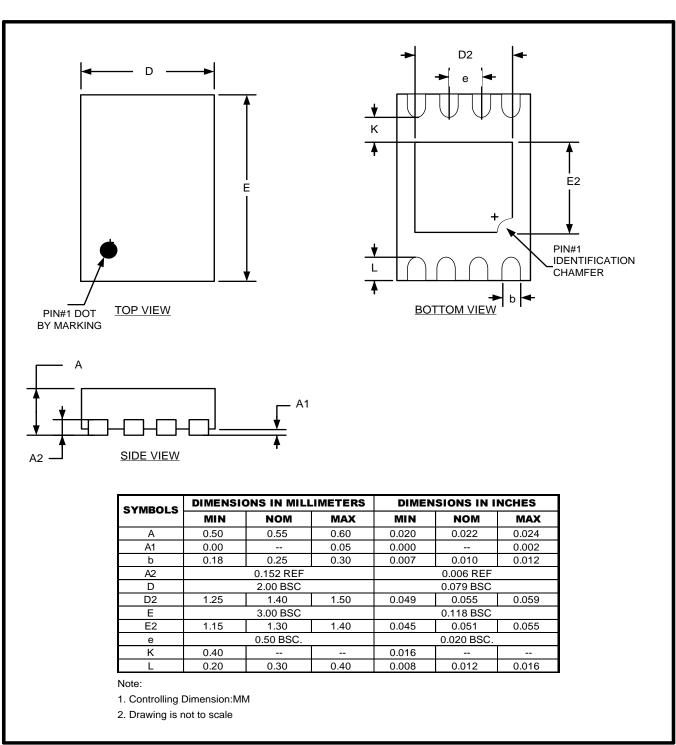

### **11. Package Information**

### 11.1 UDFN

### 8L 2x3mm UDFN Package Outline

### **12. Revision History**

| Revision | Date      | Descriptions         |

|----------|-----------|----------------------|

| A0       | Dec. 2010 | Initial version      |

| A1       | Mar. 2011 | New datasheet format |